- 32-bit paging: CR0.PG = 1 & CR4.PAE = 0 (section 4.3)

- CR0.WP

- CR4.PSE

- CR4.PGE

- CR4.SMEP

- CR4.SMAP

- PAE paging; CR0.PG = 1 & CR4.PAE = 1 & IA32_EFER.LME = 0 (section 4.4)

- CR0.WP

- CR4.PGE

- CR4.SMEP

- CR4.SMAP

- IA32_EFER.NXE

- 4-level paging: CR0.PG = 1 & CR4.PAE = 1 & IE32_EFER.LME = 1 (section 4.5)

- CR0.WP

- CR4.PGE

- CR4.PCIDE

- CR4.SMEP

- CR4.SMAP

- CR4.PKE

- IA32_EFER.NXE

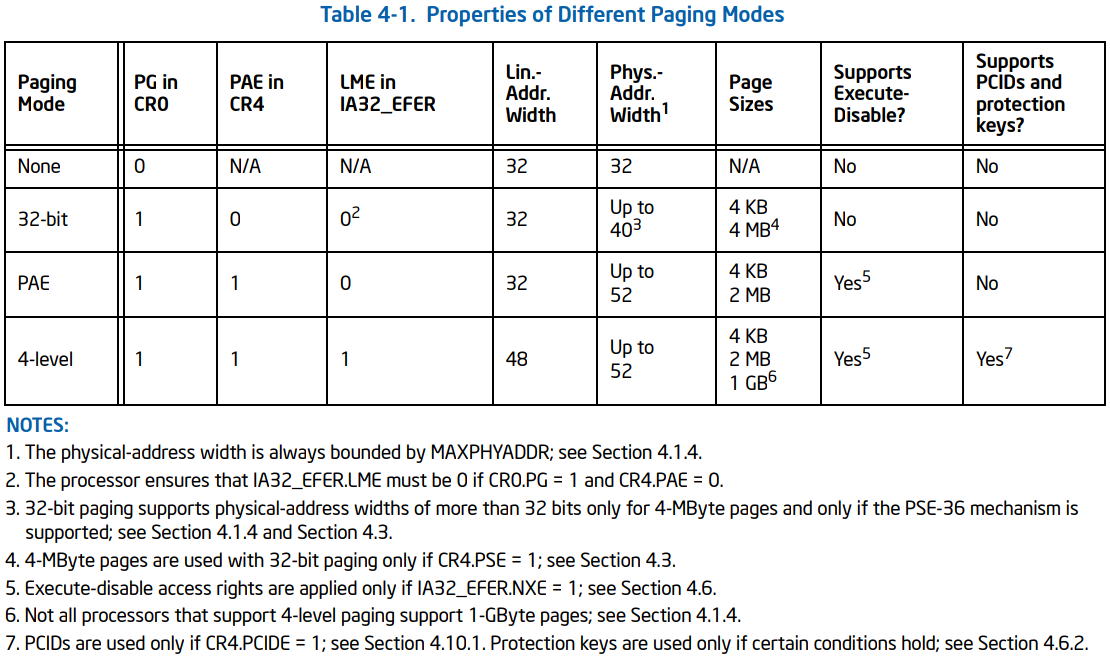

三種不同的 paging model 有這些不同的差異:

- Linear-address 寬度

- Physical-address 寬度

- Page size

- 對 execute-disable access rights 的支援

- 對 PCIDs 的支援

- 對 protection keys 的支援

4.1.3 Paging-Mode Modifies

- The WP flag in CR0 (bit 16).

- The PSE, PGE, PCIDE, SMEP, SMAP, and PKE flags in CR4 (bit 4, bit 7, bit 17, bit 20, bit 21, and bit 22 respectively).

- The NXE flag in the IA32_EFER MSR (bit 11).

Leave a Reply